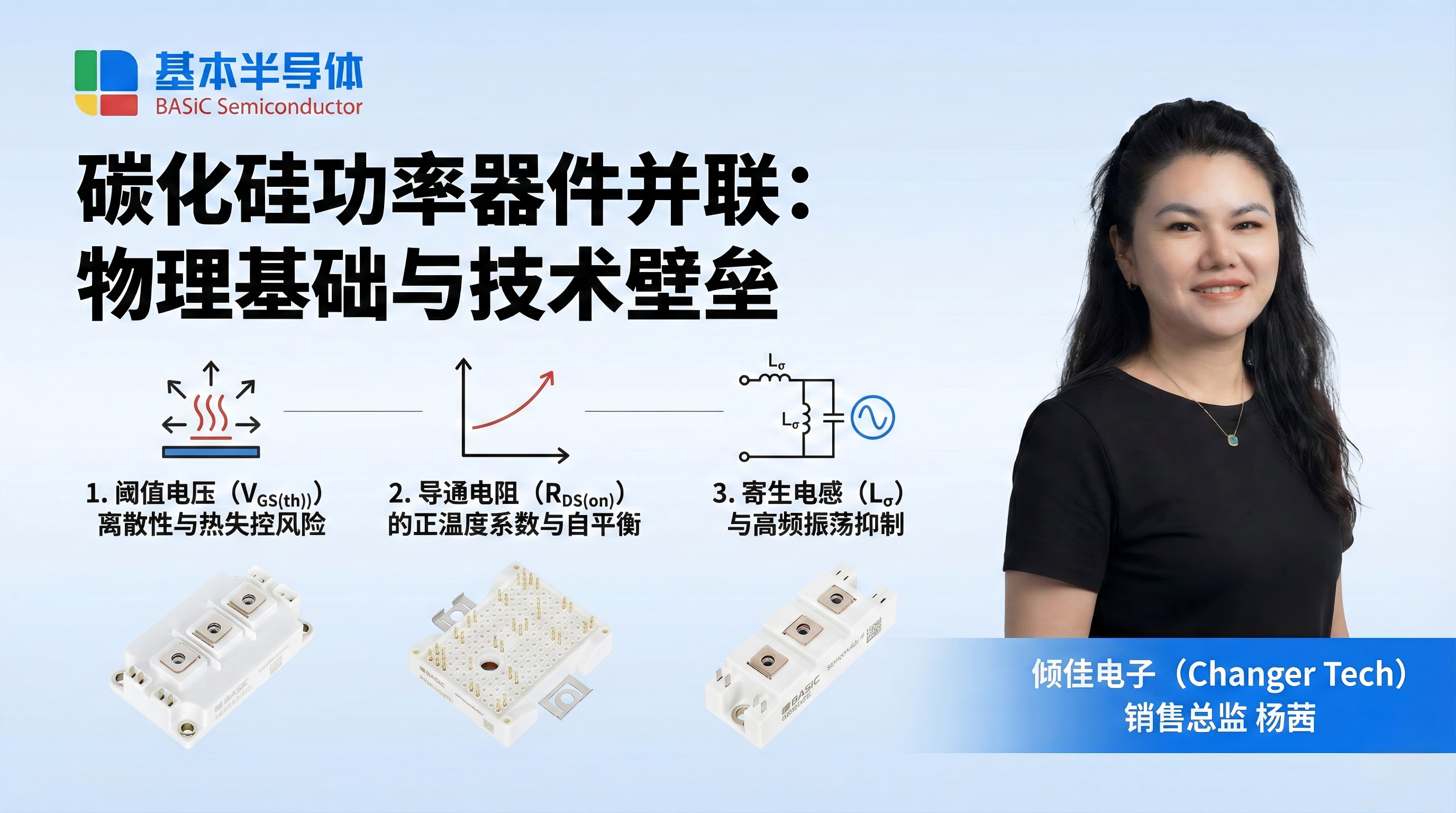

深度解析SiC碳化硅MOSFET功率模块并联技术:基于基本半导体产品矩阵的交错与硬并联策略全景研究

BASiC Semiconductor基本半导体一级代理商倾佳电子(Changer Tech)是一家专注于功率半导体和新能源汽车连接器的分销商。主要服务于中国工业电源、电力电子设备和新能源汽车产业链。倾佳电子聚焦于新能源、交通电动化和数字化转型三大方向,代理并力推BASiC基本半导体SiC碳化硅MOSFET单管,SiC碳化硅MOSFET功率模块,SiC模块驱动板等功率半导体器件以及新能源汽车连接器。

倾佳电子杨茜致力于推动国产SiC碳化硅模块在电力电子应用中全面取代进口IGBT模块,助力电力电子行业自主可控和产业升级!

倾佳电子杨茜咬住SiC碳化硅MOSFET功率器件三个必然,勇立功率半导体器件变革潮头:

倾佳电子杨茜咬住SiC碳化硅MOSFET模块全面取代IGBT模块和IPM模块的必然趋势!

倾佳电子杨茜咬住SiC碳化硅MOSFET单管全面取代IGBT单管和大于650V的高压硅MOSFET的必然趋势!

倾佳电子杨茜咬住650V SiC碳化硅MOSFET单管全面取代SJ超结MOSFET和高压GaN 器件的必然趋势!

1. 引言:宽禁带半导体时代的功率扩展挑战

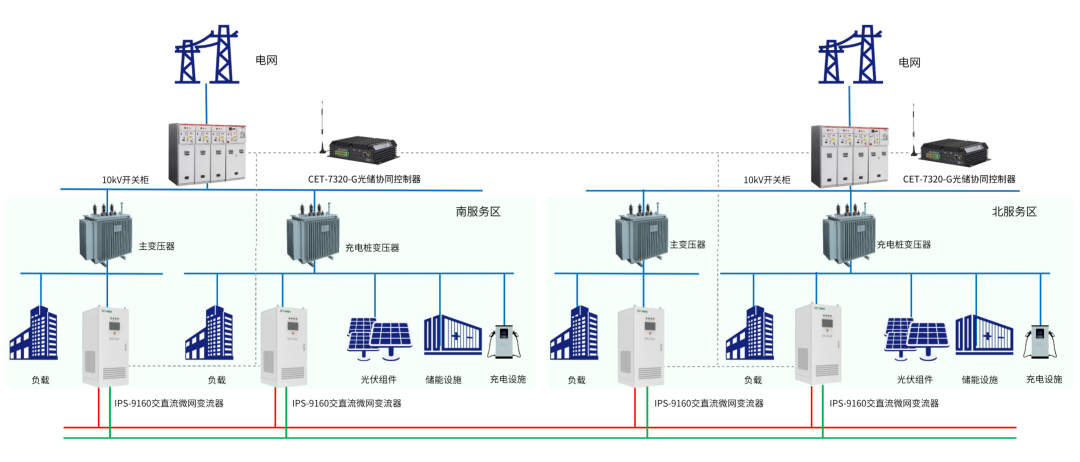

随着全球能源结构的转型与电气化进程的加速,电力电子系统正向着更高效率、更高功率密度和更高可靠性的方向飞速演进。在这一宏大的技术变革中,碳化硅(Silicon Carbide, SiC)作为第三代半导体的代表,凭借其禁带宽度大、临界击穿场强高、热导率高以及电子饱和漂移速度快等物理特性,正在逐步取代传统的硅基IGBT(绝缘栅双极型晶体管)和MOSFET,成为固态变压器SST、储能变流器PCS、Hybrid inverter混合逆变器、户储、工商业储能PCS、构网型储能PCS、集中式大储PCS、商用车电驱动、矿卡电驱动、风电变流器、数据中心HVDC、AIDC储能、服务器电源、重卡电驱动、大巴电驱动、中央空调变频器、光伏储能、轨道交通及智能电网等核心领域的关键功率器件 。

然而,SiC MOSFET芯片的制造工艺极其复杂,受限于晶圆缺陷密度和良率成本,单颗SiC芯片的电流通流能力(Current Rating)往往受到物理尺寸的限制 。当前,商业化量产的单芯片电流能力通常在几十安培至一百安培量级。面对兆瓦级(MW)的光伏逆变器、数百千瓦(kW)的超级充电桩以及高性能电驱系统对数千安培电流的需求,单一芯片或单一标准模块往往无法满足设计要求。因此,功率器件的并联技术成为了释放SiC潜能、实现功率扩展的必由之路。

并联技术在拓扑架构上主要分为两大流派:硬并联(Hard Parallel Connection)与交错并联(Interleaved Parallel Connection) 。前者追求控制的简约与系统的紧凑,试图将多个器件“虚拟”为一个大容量开关;后者则通过相位的错位,追求纹波的抵消与无源元件的极致优化。

倾佳电子杨茜将立足于**基本半导体(BASiC Semiconductor)**现有的SiC模块产品矩阵——涵盖高性能Pcore™2 ED3系列、标准工业级62mm系列、紧凑型Pcore™2 E2B系列以及34mm系列——对这两种并联策略进行深度的理论剖析与工程实证分析。我们将透过微观的芯片参数(如VGS(th)、RDS(on)温度系数)、中观的封装寄生参数(杂散电感Lσ、热阻Rth),以及宏观的系统成本与效率模型,为您揭示在不同应用场景下,如何通过精准的产品选型与拓扑匹配,构建最优的SiC功率系统。

2. 碳化硅功率器件并联的物理基础与技术壁垒

在深入探讨具体的并联拓扑之前,必须从半导体物理和封装工程的角度,理解制约SiC MOSFET并联性能的核心要素。与硅基器件相比,SiC的高速开关特性既是其优势,也是并联设计中的最大挑战。

2.1 阈值电压(VGS(th))的离散性与负温度系数

在并联系统中,电流的动态均流(Dynamic Current Sharing)主要受开通与关断时刻的同步性影响。SiC MOSFET的阈值电压VGS(th)是决定开关动作起始点的关键参数。

制造工艺导致的离散性: 受限于SiC/SiO2界面的陷阱电荷密度控制难度,SiC MOSFET的VGS(th)往往存在较大的工艺偏差。以基本半导体BMF540R12KA3模块为例,其规格书显示在Tvj=25∘C时,阈值电压的典型值为2.7V,但分布范围可从最小值2.3V延伸至最大值3.5V,偏差高达1.2V 。

负温度系数(NTC)效应: 与IGBT不同,SiC MOSFET的VGS(th)通常随温度升高而降低。这意味着,如果并联模块中某一个器件的结温(Tj)较高,其阈值电压会进一步降低,导致该器件在下一次开关周期中更早开通、更晚关断。

正反馈风险: 这种特性会形成危险的正反馈循环:温度高 → VGS(th)降低 → 开关过程承担更多电流积分(即开关损耗Esw增加) → 温度进一步升高 。这种动态热失控风险是SiC硬并联设计中必须通过严格筛选(Binning)或主动门极控制来解决的首要难题。

2.2 导通电阻(RDS(on))的正温度系数与静态均流

静态均流(Static Current Sharing)取决于并联支路的阻抗匹配。在这方面,SiC MOSFET表现出优于IGBT的特性。

PTC特性分析: SiC MOSFET是多数载流子器件,其导通电阻RDS(on)具有显著的正温度系数(PTC)。以基本半导体BMF540R12MZA3(ED3封装)为例,其RDS(on)典型值从25°C时的2.2 mΩ上升至175°C时的约4.8-5.2 mΩ,增长倍率约为2.2倍左右 。

自平衡机制: 当并联模块中的某一支路因内阻较小而分流了更多电流时,其结温上升会迅速推高RDS(on),迫使电流向其他低温支路转移。这种物理层面的负反馈机制(Negative Feedback)天然地促进了静态电流的平衡,降低了对静态参数筛选的极端要求 。

2.3 寄生电感(Lσ)与高频振荡

SiC器件的开关速度(di/dt)极快,通常可达数kA/μs。根据法拉第电磁感应定律 Vovershoot=Lσ⋅dtdi,极小的杂散电感也会产生巨大的电压尖峰。

不对称性的放大: 在并联回路中,如果各支路的杂散电感不一致(Lσ1=Lσ2),电感较小的支路将承担更快的电流变化率,导致动态电流严重失衡。

门极振荡: 功率回路的杂散电感会通过源极公共端耦合到门极回路,形成LC振荡网络。在硬并联中,多个低阻抗的门极回路并联,极易在米勒平台区域诱发高频环流,甚至导致误导通 。

3. 基本半导体SiC模块产品矩阵深度解析

针对不同的并联需求,基本半导体构建了层次分明的产品矩阵。我们将重点分析Pcore™2 ED3、62mm工业封装以及Pcore™2 E2B系列,剖析其在封装设计上如何应对并联挑战。

3.1 Pcore™2 ED3系列:为硬并联而生的旗舰

代表型号: BMF540R12MZA3

关键参数: 1200V / 540A / RDS(on)≈2.2mΩ

ED3系列是基本半导体针对高端工业应用(如储能PCS、固态变压器)推出的高性能模块,其设计哲学完全服务于高功率密度的硬并联应用。

3.1.1 氮化硅(Si3N4)AMB基板的机械与热学优势

在硬并联系统中,由于总功率巨大,热应力循环对模块的可靠性提出了极高要求。BMF540R12MZA3采用了Si3N4 AMB(活性金属钎焊)陶瓷基板,而非传统的Al2O3(氧化铝)或AlN(氮化铝)。

机械强度: Si3N4的抗弯强度高达700 N/mm2,远超AlN(350 N/mm2)和Al2O3(450 N/mm2)。这种高强度使得基板厚度可以减薄至360 μm (通常AlN需630 μm) 。

热阻优化: 虽然Si3N4的本征热导率(90 W/mK)低于AlN(170 W/mK),但由于厚度减半,其最终的热阻表现与AlN基板相当,同时彻底解决了AlN脆性大、易在温度冲击下发生铜层剥离(Delamination)的问题 。

并联意义: 在多模块并联的大功率工况下,热循环剧烈。Si3N4基板保证了模块在数千次并联启停循环后,仍能保持极低的结-壳热阻(Rth(j−c)),防止因个别模块热失效导致的系统性崩溃。

3.1.2 低感封装与布局

ED3封装降低了模块内部的杂散电感。这对于硬并联至关重要,因为它允许设计者在外部母排设计上拥有更大的容错空间,同时减少了并联模块间的动态不平衡电压 。

3.2 62mm工业模块:传统升级的过渡之选

代表型号: BMF540R12KA3

关键参数: 1200V / 540A / Lσ=30nH 6

62mm封装是电力电子领域的“老兵”,基本半导体的BMF540R12KA3将SiC芯片植入这一经典封装,主要目的是为了兼容替代。

并联局限性: 30nH的杂散电感在SiC的高频应用中属于较高水平。62mm模块主要采用螺丝端子连接,这种结构在硬并联时很难做到各支路电感的绝对对称 。

应用策略: 该模块适合对开关速度要求不极端、但需要利用现有机械结构进行升级的场合。在并联使用时,必须配合较大的外部栅极电阻(Rg)来限制di/dt,从而牺牲部分开关损耗以换取系统稳定性。

3.3 Pcore™2 E2B系列:交错并联的灵巧积木

代表型号: BMF240R12E2G3

关键参数: 1200V / 240A / 内置SiC SBD

E2B系列(兼容EasyPACK™ 2B)是模块化设计的典范,特别适合交错并联架构。

内置SBD的决定性优势: BMF240R12E2G3集成了SiC肖特基二极管(SBD)。在交错并联的DC-DC变换器(如Buck/Boost)中,死区时间内主要依靠二极管续流。SiC MOSFET的体二极管(Body Diode)通常存在较高的导通压降(VSD≈4.9V for ED3 without SBD 6)和一定的反向恢复风险。而内置SBD将VSD降低至更低水平(约1.9V 6),且几乎无反向恢复电荷(Qrr≈0)。

并联意义: 这种特性使得E2B模块在交错并联的高频硬开关应用中,效率显著高于仅依靠体二极管的大功率模块,极大地降低了开关损耗(Eon)和电磁干扰(EMI)。

4. 硬并联(Hard Parallel):极致功率的暴力美学

硬并联是指将多个SiC模块的门极、漏极和源极直接(或通过微小阻抗)连接在一起,共用一套直流母线和驱动信号。这种拓扑在兆瓦级光伏逆变器、风电变流器和重型牵引驱动中占据主导地位。

4.1 硬并联的核心优势分析

4.1.1 控制架构的极简性

在硬并联系统中,无论并联了多少个模块(例如4个BMF540R12MZA3),控制器(MCU/DSP)仅将其视为一个等效的2160A大电流开关。

控制资源节省: 无需增加PWM通道数,无需复杂的相位同步算法,无需多路独立的电流采样与闭环控制。这对于追求高可靠性和低软件复杂度的工业控制系统至关重要 。

驱动同步: 虽然需要增强驱动功率,但信号逻辑是统一的,避免了交错控制中可能出现的节拍错乱风险。

4.1.2 磁性元件的成本与体积优化

硬并联系统通常在交流输出端共用一套滤波电感(L)或LCL滤波器。

规模效应: 根据磁性元件设计原理,制造一个能够承受2000A的大电感,通常比制造4个承受500A的小电感在铜耗、铁芯材料成本和体积上更具优势。

结构简化: 减少了电缆连接点和结构件,降低了系统的装配复杂度和潜在的机械故障点 。

4.1.3 利用RDS(on)正温度系数实现静态均流

如前所述,基本半导体的SiC模块具有显著的RDS(on)正温度系数。

实测数据支撑: BMF540R12MZA3的内阻从25°C的2.6 mΩ升至175°C的5.2 mΩ 。

机制: 假设模块A初始内阻低,分流大 → 模块A温度升得快 → 模块A内阻迅速增加 → 电流自动向模块B转移。这种强烈的自平衡能力使得SiC硬并联在稳态大电流工作下非常稳定,优于某些IGBT方案 。

4.2 硬并联的技术挑战与解决方案

4.2.1 动态均流与Vth筛选

硬并联的阿喀琉斯之踵在于开关瞬态。由于Vth的负温度系数,如果不加干预,热失控在微秒级的开关过程中就可能发生。

解决方案: 必须对并联的模块进行Vth分档(Binning)。基本半导体建议并联模块间的Vth差异控制在0.2V以内 。

驱动策略: 采用独立栅极电阻(Split Gate Resistors) 。每个模块必须配备独立的Rg(on)和Rg(off)。这不仅可以微调开关速度以补偿参数差异,还能有效阻断模块间门极回路的环流,防止高频振荡 。

4.2.2 杂散电感对称性设计

对于SiC MOSFET,母排设计的对称性要求达到了苛刻的程度。

蝴蝶型布局(Butterfly Layout): 推荐采用完全对称的“蝴蝶型”直流母线设计,确保从电容组到每个模块的物理路径长度、阻抗完全一致 。

ED3的优势: ED3封装的端子布局经过优化,更容易实现低感叠层母排的连接,相比62mm封装,能显著降低换流回路中的Lσ,从而抑制关断过压,允许更快的开关速度。

4.2.3 驱动回路的米勒钳位(Miller Clamp)

在硬并联中,当一个模块快速开通时,其产生的dv/dt会通过米勒电容Crss耦合到并联模块的栅极。

风险: 由于并联导致总栅极阻抗变化,这种干扰极易引起误导通(Crosstalk Shoot-through)。

BASiC方案: 基本半导体在ED3驱动方案中强烈推荐使用带米勒钳位功能的驱动芯片(如BTD5350),在关断期间将栅极低阻抗拉地,彻底消除误导通风险 。

5. 交错并联(Interleaved Parallel):效率与纹波的精算师

交错并联是指将多个相同的功率变换单元(如Boost Converter)并在输入输出端,但在控制上保持相位的错开(例如双路交错相差180°,三路交错相差120°)。这种方案常用于光伏MPPT、储能DC-DC和充电桩PFC级。

5.1 交错并联的核心优势分析

5.1.1 纹波抵消与无源元件小型化

这是交错并联最本质的优势。

频率倍增效应: N相交错使得总输入/输出电流的纹波频率变为单相开关频率的N倍,而纹波幅值大幅下降(甚至在特定占空比下理论为零) 。

滤波器瘦身: 这意味着可以使用更小感值的电感和更小容量的电容。对于SiC系统,如果单相频率为50kHz,4相交错后等效频率达200kHz,这使得采用极小体积的磁粉芯电感成为可能,极大提升了系统的功率密度 。

5.1.2 热分布均匀与冗余性

物理去耦: 每个相位都有独立的电感和功率模块(如独立的BMF240R12E2G3)。热源在空间上是分散的,避免了硬并联中热量集中的“热岛效应”,降低了散热器设计的难度 。

N-1冗余: 如果其中一路模块失效,控制系统可以切断该路,调整其余相位的角度和电流基准,使系统降额运行。这对于要求高可用性的数据中心UPS或储能电站至关重要。

5.1.3 轻载效率优化(切相控制)

储能系统和光伏逆变器往往长时间工作在轻载状态。

切相策略: 交错并联允许在轻载时关闭部分相位。例如,在10%负载下,只保留一路运行。这消除了其他几路的开关损耗和铁损,使系统始终工作在器件的最佳效率区间 。

SiC E2B的优势: BMF240R12E2G3模块的小电流规格(240A)非常适合这种精细化的能量管理。相比之下,使用540A的大模块在几十安培负载下工作,其开关损耗占比将过大,效率低下。

5.2 交错并联的技术挑战

5.2.1 系统复杂度的指数级上升

控制成本: 需要更多的PWM资源、ADC采样通道和更复杂的电流平衡算法。

驱动成本: 每一路都需要独立的隔离电源和驱动电路。对于4路交错,驱动成本是硬并联(共用驱动)的近4倍。

5.2.2 环流问题

如果各相电感值偏差较大或占空比控制不精细,相位之间会产生严重的环流,导致额外的导通损耗并可能使磁性元件饱和。这要求电感的一致性非常好,或者在控制算法中加入极其快速的均流环 。

6. 综合对比分析与选型策略

为了更直观地展示两种策略的差异,我们将从多个维度进行对比,并结合基本半导体产品给出建议。

6.1 性能维度对比表

| 维度 | 硬并联 (Hard Parallel) | 交错并联 (Interleaved) | 优势方 |

|---|---|---|---|

| 电流扩展能力 | 线性增加,适合超大电流 | 受限于电感体积和控制算力 | 硬并联 |

| 输出纹波 | 较大,需大滤波器 | 极小,频率倍增 | 交错并联 |

| 控制复杂度 | 低 (单路PWM) | 高 (多路PWM+均流) | 硬并联 |

| 热管理 | 集中发热,需强力散热 | 分散发热,易于处理 | 交错并联 |

| 轻载效率 | 较低 (无法切相) | 极高 (支持切相) | 交错并联 |

| 器件要求 | 需严格配对 (Vth),高对称布局 | 参数容忍度高,独立控制 | 交错并联 |

| 系统成本 | 硅成本低,磁性元件成本高 | 硅/驱动成本高,磁性元件成本低 | 视频率而定 |

| EMI特性 | di/dt叠加,干扰大 | 纹波抵消,干扰频谱分散 | 交错并联 |

6.2 基于基本半导体产品的应用场景推荐

场景一:兆瓦级集中式储能变流器 / 重卡电驱动

推荐策略: 硬并联

核心模块: Pcore™2 ED3 (BMF540R12MZA3)

深度理由: 在这些应用中,总功率极大(>500kW),如果采用交错并联,所需的电感数量和体积将不可接受。ED3模块的高电流(540A)、Si3N4基板的高可靠性以及低感封装设计,完美契合硬并联对大电流、高可靠性和紧凑布局的需求。利用其RDS(on)的正温度系数实现自然均流,通过严格的母排对称设计和驱动Miller Clamp解决动态问题。

场景二:储能DC-DC变换器 / 充电桩功率模块

推荐策略: 交错并联

核心模块: Pcore™2 E2B (BMF240R12E2G3)

深度理由: 此类应用追求极高的加权效率(如CEC效率)和功率密度。E2B模块内置的SiC SBD消除了交错Boost/Buck拓扑中高频硬开关的二极管反向恢复损耗 6。通过3-4路交错,可以将等效开关频率提升至数百kHz,大幅减小储能电感的体积和成本。同时,利用切相控制,确保在夜间或涓流充电等轻载工况下依然保持高效。

场景三:老旧设备升级 / 中功率通用变频器

推荐策略: 硬并联 (有限数量)

核心模块: 62mm (BMF540R12KA3)

深度理由: 为了兼容旧有的IGBT结构,62mm模块是最佳选择。虽然其杂散电感(30nH)较ED3略高,限制了极限开关速度,但通过适当增大Rg并采用硬并联(通常不超过2并),可以在不改变机械结构的前提下显著提升系统效率。

7. 结论与展望

碳化硅功率模块的并联技术并非简单的“连连看”,而是一项涉及芯片物理、封装力学、电磁场理论和控制算法的系统工程。

硬并联是通往极致功率的捷径,它依赖于基本半导体ED3系列这样采用先进Si3N4基板和低感设计的模块,通过物理层面的强壮性来对抗大电流带来的热与电磁冲击。

交错并联则是通往极致效率的巧径,它发挥了基本半导体E2B系列内置SBD的小巧灵活优势,通过控制层面的精细化运作,以空间(多相)换取时间(高频),实现了系统体积与损耗的双重缩减。

对于设计者而言,选择哪种策略,取决于对系统功率密度、效率曲线、控制成本以及可靠性目标的综合权衡。基本半导体丰富的产品矩阵,从重载的ED3到灵巧的E2B,为这两种策略的落地提供了坚实的器件基础。未来,随着SiC芯片成本的进一步下降和驱动技术的智能化(如动态有源均流),并联技术将更加成熟,推动电力电子装置向着更高维度的性能迈进。

审核编辑 黄宇

- 随机文章

- 热门文章

- 热评文章

- 朱婷宣布将在世联赛期间回归中国女排 曾提出退役申请

- 努比亚“AI FOR ALL”三款新品发布 开启全民AI体验

- 坐拥超5.2亿用户 中国电信促物联网应用走深走实

- 开门红!一季度全国演出市场场次、票房、观演人数均同比增长

- 与《黑神话:悟空》联动 海信电视E8N系列新品发布

- 分红比例、资产质量、存量理财,浙商银行管理层回应多个热点问题

- 新门派峨眉!《剑侠世界:起源》峨眉论剑资料片今日8点上线

- ATFX汇市:欧元区和美国的制造业PMI将发布,市场预期乐观

- “疫苗茅”智飞生物暴跌15%!什么情况?多只明星基金已提前减仓

- 超燃!港股尾盘攻势不减,港股互联网ETF(513770)涨近4%!续刷年内新高!

- 涉嫌试图推翻2020年美总统竞选结果 多人受重罪指控

- 中央气象台:西北地区有沙尘天气

- 宗校立:美国一季度GDP增速显著放缓,这是苦肉计!

- 1“赛事+”提升城市“流量” 陕西商洛拓经济发展新“赛道”

- 2“五一”临近 持基过节的投资者要注意这几点

- 3华发股份:成功入选“人民优选”品牌 五一黄金周热销30亿

- 4钟鼓楼老街区的古都新事

- 5非常危险!女子摔成粉碎性骨折!又是因为洞洞鞋,夏天多人中招……

- 6金税四期试点上线,财税体制改革拉开帷幕!或有资金借道信创ETF基金(562030)逢跌进场布局

- 7到2027年产业规模达到2000亿元 浙江发布历史经典产业高质量发展计划

- 8初步数据:我国一季度经常账户顺差392亿美元

- 9IDC:24Q1全球PC出货量恢复增长 达到疫情前水平

- 10“发现山西之美”TDC旅游发现者大会举办:共话文旅新生态 邀客体验新玩法

- 11国门“夫妻档” 国庆共坚守

- 12北交所一周审核动态:2家企业更新进展 胜业电气二轮问询回复中称家电头部客户对价格敏感度较低

- 13(中国新貌)“国宝”大熊猫:栖居更美境 云游更广天

- 1大裁员下,特斯拉两名顶级高管离职

- 2奇瑞将与欧洲高端品牌签署技术平台授权协议

- 32024中国长三角青年企业家交流大会在杭州举办

- 4雷克萨斯GX中东版 全部在售 2023款 2022款 2020款 2019款 2018款成都远卓名车雷克萨斯GX中东版团购钜惠20万 欢迎上门试驾

- 5零跑C16将搭载中创新航磷酸铁锂电池

- 6Q1净利微增7%,宁德时代股东总数较2023年年末减少10728户

- 7哪吒,需要背水一战

- 8“新”中有“机”!创新服务承接新流量 撬动消费升级

- 9非创始版SU7何时交付 小米:工厂生产爬坡 全力提高产能

- 10央媒评卧铺挂帘:谁买的票谁做主

- 11江西南昌首部“多规合一”国土空间总体规划获批

- 12方程豹旗舰硬派越野!豹8正式亮相:仰望U8“青春版”登场

- 13583家族/造型霸气 方程豹豹8量产版发布