随着多核片上系统 (SoC) 的复杂性不断增加,SoC 调试变得越来越具有挑战性。这些系统的软件调试和优化工作正在不断升级,从而增加了开发时间、工作量和成本。现在迫切需要更高效、更具可扩展性的调试方法来帮助工程师快速发现并解决硬件和实时软件问题。

Tessent UltraSight-V 是用于 RISC-V 调试和跟踪的完整端到端解决方案,其设计符合官方 RISC-V E-Trace 规范。该嵌入式 IP 和软件解决方案提供全面、高效的调试和跟踪功能,这些功能可与行业标准工具集成,帮助嵌入式软件工程师开发高性能嵌入式软件。

Tessent UltraSight-V 是 Tessent 嵌入式分析产品系列的一部分,采用了高效的非侵入式技术,例如基于高效跟踪 (E-Trace) 标准的高度压缩编码处理器跟踪、日志记录、高速接口(USB 2.0) 和 DMA,以实现快速代码上传。该解决方案极大限度限度地减少了调试延迟,加快了 SoC 项目的进程,从而使您能够在市场截止日期前完成上市过程。

RISC-V 处理器的高度压缩跟踪解决方案

复杂系统容易出现不理想的软件行为。Tessent UltraSight-V 的增强型跟踪编码器 (ETE) 提供了一种实时监控 CPU 程序执行的机制。它可对指令执行过程(可选地为数据内存访问过程)进行编码。它还能够以高度压缩的格式输出跟踪,从而大幅节省了带宽,在大型复杂系统中尤为如此。设备执行可以完全离线重建。非侵入式 ETE 的工作延迟极小,因此不会影响性能。

筛选跟踪可以帮助您进一步调查问题。增强型跟踪编码器支持 E-Trace 规范中的所有强制和选配功能。它还可以提供周期精确的跟踪,从而为软件性能优化提供见解。

RISC-V 处理器的完整调试和跟踪解决方案

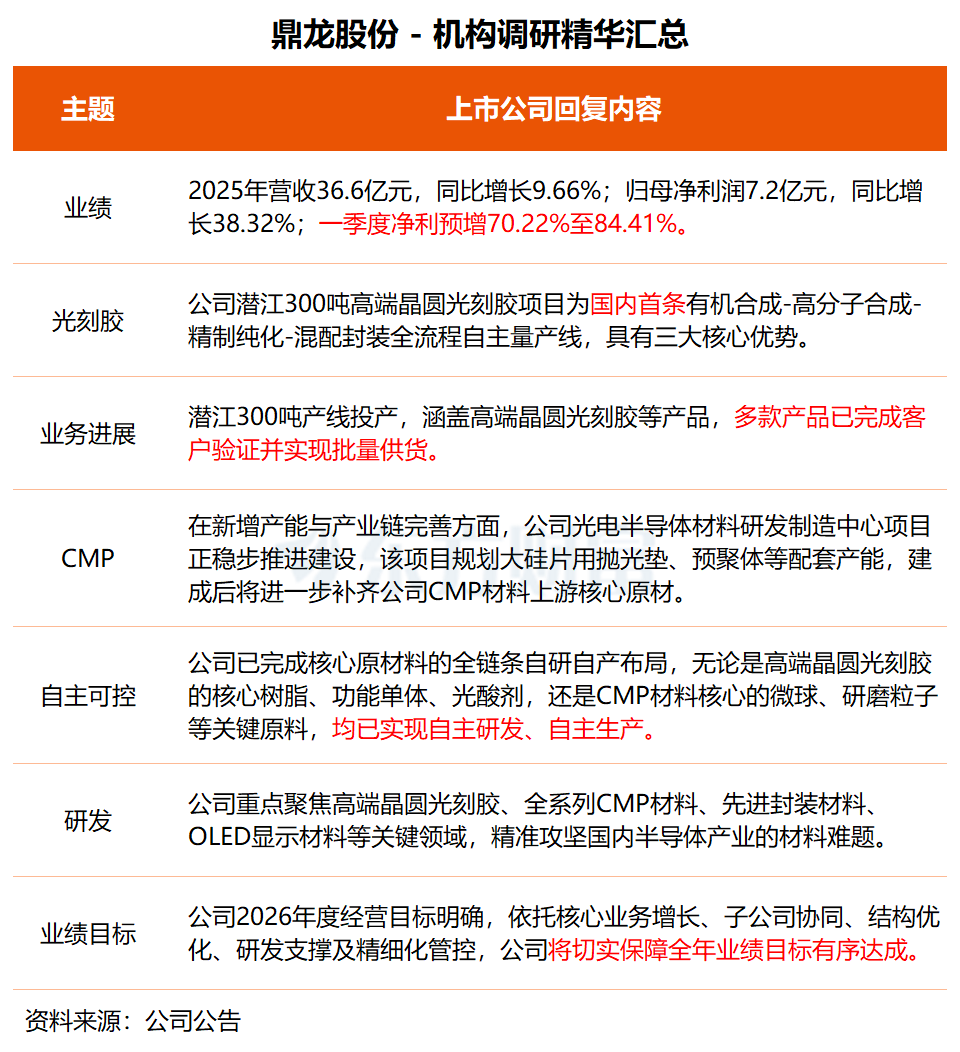

Tessent UltraSight-V 包括一组 IP 模块和主机软件,它们对软件应用程序在系统中的行为方式具有广泛可见性。处理器分析模块提供运行控制功能。借助直接内存访问 IP 模块可将代码上传到 SoC,其速度为正常 GDB 加载速度的 70-100 倍。借助静态仪器 IP 模块,可通过数量仅为原来二十分之一的指令完成带时间戳的 printf 风格调试。虚拟控制台模块于在目标上运行的软件和调试主机之间提供了一个双向通信通道。它取代了传统的基于 UART 的通信,无需额外的物理端口。可扩展的专用基础设施可确保实现非侵入式监控。该基础设施可通过 USB、JTAG 或 PCIe 接口访问(见图1)。UltraSight-V 中的主机软件与 GDB、OpenOCD 和 VS Code 等常见 IDE 集成(见图2)。

▲ 图 1

▲ 图 2

总结

综上所述,Tessent UltraSight-V 是面向 RISC-V 处理器的全面调试和跟踪解决方案,它结合了嵌入式 IP 和软件,能够实现高效的调试和跟踪,同时还与行业标准工具集成,为高性能嵌入式软件的开发提供支持。

要点包括:

它是 RISC-V 调试和跟踪的完整解决方案。

它的设计符合官方 RISC-V 跟踪规范。

它是由嵌入式 IP 和软件组成的端到端解决方案。

它提供了全面、高效的调试和跟踪功能。

它与行业标准工具集成。

它使得嵌入式软件工程师能够开发高性能嵌入式软件。

Tessent UltraSight-V 的功能体现了西门子在 RISC-V 调试和跟踪解决方案方面的深厚专业知识和领先地位。

如需了解 Tessent UltraSight-V 和西门子 EDA 的其他嵌入式分析解决方案的详细信息,请点击此处查阅。

- 随机文章

- 热门文章

- 热评文章

- 知未智能开发多智能体KenSho,可分析产业链、预测商业影响

- 嘉银科技:金融科技助推金融业务全流程数智化转型

- 美债收益率攀升、鲍威尔转变态度!黄金迎来新一轮挑战还是机会?

- 分红比例、资产质量、存量理财,浙商银行管理层回应多个热点问题

- 巴勒斯坦“入联”申请遭美否决,中方表态

- 中国人民解放军信息支援部队成立大会在京举行 习近平向信息支援部队授予军旗并致训词

- 坦桑尼亚持续暴雨已致66人遇难

- TMGM每日市场(04月22日)

- 和谐共生|解码“地球之肾”,中国湿地何以美出圈?

- 突发!一移民船在吉布提附近海域倾覆 至少16死28失踪

- 单周大跌10%,重仓英伟达巨亏?但斌回应!

- 6年5次增资!又见小微公募"输血"

- 广西桂林市政协原副主席陆智成被“双开”

- 1“赛事+”提升城市“流量” 陕西商洛拓经济发展新“赛道”

- 2“五一”临近 持基过节的投资者要注意这几点

- 3华发股份:成功入选“人民优选”品牌 五一黄金周热销30亿

- 4钟鼓楼老街区的古都新事

- 5金税四期试点上线,财税体制改革拉开帷幕!或有资金借道信创ETF基金(562030)逢跌进场布局

- 6到2027年产业规模达到2000亿元 浙江发布历史经典产业高质量发展计划

- 7非常危险!女子摔成粉碎性骨折!又是因为洞洞鞋,夏天多人中招……

- 8初步数据:我国一季度经常账户顺差392亿美元

- 9IDC:24Q1全球PC出货量恢复增长 达到疫情前水平

- 10“发现山西之美”TDC旅游发现者大会举办:共话文旅新生态 邀客体验新玩法

- 11国门“夫妻档” 国庆共坚守

- 12北交所一周审核动态:2家企业更新进展 胜业电气二轮问询回复中称家电头部客户对价格敏感度较低

- 13(中国新貌)“国宝”大熊猫:栖居更美境 云游更广天

- 1大裁员下,特斯拉两名顶级高管离职

- 2奇瑞将与欧洲高端品牌签署技术平台授权协议

- 32024中国长三角青年企业家交流大会在杭州举办

- 4雷克萨斯GX中东版 全部在售 2023款 2022款 2020款 2019款 2018款成都远卓名车雷克萨斯GX中东版团购钜惠20万 欢迎上门试驾

- 5零跑C16将搭载中创新航磷酸铁锂电池

- 6Q1净利微增7%,宁德时代股东总数较2023年年末减少10728户

- 7哪吒,需要背水一战

- 8“新”中有“机”!创新服务承接新流量 撬动消费升级

- 9非创始版SU7何时交付 小米:工厂生产爬坡 全力提高产能

- 10央媒评卧铺挂帘:谁买的票谁做主

- 11江西南昌首部“多规合一”国土空间总体规划获批

- 12方程豹旗舰硬派越野!豹8正式亮相:仰望U8“青春版”登场

- 13583家族/造型霸气 方程豹豹8量产版发布