本教程在 Ubuntu22.04.1 虚拟机中安装了 Xilinx 2024.1 的开发环境,基于该环境从源码编译 PYNQ 3.1.2 工程,生成能够在 ALINX AXU15EGB 开发板上运行的 PYNQ 系统镜像。

Zynq US+ MPSoC AI SFP+ 10G 光纤 FPGA 开发板AXU15EGB

AXU15EGB 开发板:

www.alinx.com/detail/261

资源链接:

https://pan.baidu.com/s/1J1KnN_z404Skze42CUj7gQ

提取码: in8s

环境配置

提示:

ubuntu、vitis 和 vivado 安装的部分可以参考 ALINX 的教程文档《course_s0_Xilinx开发环境安装教程》,虽然版本不一样,但流程基本不变;安装 2024.1 版本的 petalinux 则需要参照本教程,petalinux 的依赖库和旧版本稍有区别。

ubuntu22.04.1 安装

1. 在 vmware 中安装 ubuntu22.04.1,可以使用资源链接中提供的 ubuntu-22.04.1-desktop-amd64.iso 镜像文件,安装过程比较简单,使用 vmware 的创建虚拟机流程安装即可。(vmware 软件建议使用较新的版本,本教程中使用的是 vmware16)

需要注意的是分配给虚拟机的资源,本教程中虚拟机资源配置如图所示。其中处理器 8 个,分配内存建议至少 16GB,硬盘存储至少 500GB。主机如果是网线直连,网络适配器就配置为桥接模式,如果是使用 wifi,就配置为 NAT 模式。(请根据自身主机的配置合理分配资源。主机留给自身的内存太少会导致主机系统卡顿甚至卡死)

进入 ubuntu22.04.1 系统,打开 Software & Updates,切换软件源为阿里云的软件源

选择 Updates,将更新自检改为 Never,为了保证环境稳定,我们不会更新系统版本。(如果系统主动弹出更新提示的窗口,建议也不要更新,直接关闭窗口)

打开一个命令行终端,输入命令,选择“No”,回车确认。这一步是将 ubuntu 默认的 shell 从 dash 改为 bash

sudo dpkg-reconfigure dash

在 ubuntu 的 Settings 中,选择 Privacy->Screen,将锁屏时间取消

Petalinux 2024.1安装

在 ubuntu 中打开一个命令行终端,输入命令,更新软件源

sudo apt-get update

输入命令,安装 petalinux 的依赖项

sudo apt-get install iproute2 gawk python3 python2 build-essential gcc git make net-tools libncurses5-dev tftpd zlib1g-dev libssl-dev flex bison libselinux1 gnupg wget git-core diffstat chrpath socat xterm autoconf libtool tar unzip texinfo zlib1g-dev gcc-multilib automake zlib1g:i386 screen pax gzip cpio python3-pip python3-pexpect xz-utils debianutils iputils-ping python3-git python3-jinja2 libegl1-mesa libsdl1.2-dev pylint

输入命令,准备 petalinux 的安装目录(注意,这里的 alinx 需要替换成自己的用户名)

sudo mkdir -p /opt/pkg/petalinux sudo chown alinx:alinx /opt/pkg/petalinux

将资源链接提供的 petalinux2024.1 安装包拷贝到 ubuntu 中,本教程拷贝到 Downloads 目录下

在 Downloads 目录下打开终端,输入如下命令,安装 petalinux。此时会出现让你查看协议的提示,按回车查看协议内容,按 q 退出协议内容,按 y 同意协议内容

chmod 755 ./petalinux-v2024.1-05202009-installer.run ./petalinux-v2024.1-05202009-installer.run -d /opt/pkg/petalinux/

安装完成后,在当前终端输入命令,测试 petalinux 环境变量配置(注意,环境变量配置只在当前终端中生效,如果打开另一个终端,需要重新配置 petalinux 环境变量)

source /opt/pkg/petalinux/settings.sh

Vivado 和 Vitis 2024.1 安装

在 ubuntu 中解压资源链接提供的 vitis 的安装压缩包

进入解压后的目录,打开终端,输入命令,运行依赖库检测脚本

sudo ./installLibs.sh

输入命令,添加执行权限,运行安装程序

sudo chmod +x xsetup

安装完成后,输入命令,修改安装目录的权限

sudo chmod 777 -R /tools/Xilinx/

输入命令,配置 vivado 环境变量,并打开 vivado(vivado 环境变量配置也仅在当前终端中生效)

source /tools/Xilinx/Vivado/2024.1/settings64.sh vivado&

软件启动后,在“Help → Manage license…”中添加 license 文件

输入命令,安装下载器驱动

cd /tools/Xilinx/Vivado/2024.1/data/xicom/cable_drivers/lin64/install_script/install_drivers/ sudo ./install_drivers

Vivado 工程参照 ALINX 教程文档 course_s2_ALINX_ZYNQ_MPSoC 开发平台 Vitis 应用教程“第一章 体验 ARM,裸机输出Hello World”中搭建 vivado 工程的部分,搭建基础的 ps_hello vivado 工程,ZYNQ Processor IP 配置已在该章节详述。完善介绍其余部分配置介绍:

启用 PL Fabric Clocks 勾选,这里预设置四个时钟频率。

Slave Interface 配置

在 PS-PL Configuration 窗口,配置 AXI HP, 勾选 AXI HP0 FPD 和 AXI HP1 FPD 设置数据位宽为 128,外连到 AXI_Interconnect_1 的 Master AXI port 以此数据位宽越大越好。

Master Interface 配置

同样在该窗口勾选 AXI HPM0 LPD 并配置数据位宽为 32

Interrupts 配置

在中断栏里启用中断请求 IRQ0, IRQ1。

其端口位宽自动是 7 也与外连端口自适应,中断敏感是上升沿。预留终端请求 0,连接 1。

GPIO EMIO 配置

在 I/O 配置栏中勾选 GPIO EMIO, MPSoC 器件最大可选 95。

将 I2C 1 设置成 EMIO 用于连接摄像头

同样勾选 UART 1 设置成 emio 类型导出引脚连接 PL 侧 UART

ALINX 向广大用户提供文档时也将出厂测试的 Vivado 工程及镜像。这篇文档是基于此工程实现,接下来介绍工程实现。

总览:工程内基于 AXU15EGB 外设接口应用众多 AMD IP 以及 ALINX IP 实现检测办法。

添加 MIPI CSI-2 Rx subsystem 模块,用于 MIPI 数据的接收和解析,转成 axi-stream 接口。配置如下,数据格式选择 YUV422, 选择 2 lane,Line Rate 配置为 1000Mbps,指的是最大支持的速率,也可以根据自己的需求填写,范围为 80-2500;Pixels Per Clock 默认配置为 1,表示 1 个周期为 1 个像素;这里配置为 2。

Shared Logic 选择“include Shared Logic in core”

Pin Assignment 根据原理图按照以下配置。

添加 subset 模块

调整图像数据顺序,因为经过实际操作发现,图像的 YUV 数据顺序需要调整。

添加 Video Processing Subsystem 模块

Sample Per Clock设置 2,Maximum Data Width:8;Maximum Number of Pixels:1920;Maximum Number of lines: 1080 再选择Color Space Conversion Only 并勾选 RGB | YUV 4:4:4 | YUV 4:2:2

添加 Video Frame Buffer Write 模块

这个 IP 类似于 VDMA IP, 将流接口转成 AXI, 按照如下配置。

添加 AXI_Ethernet 模块

在 Physical Interface 栏勾选 1Gbps,Physical Interface Selection 选 RGMII

Mac Features 里选择 4k

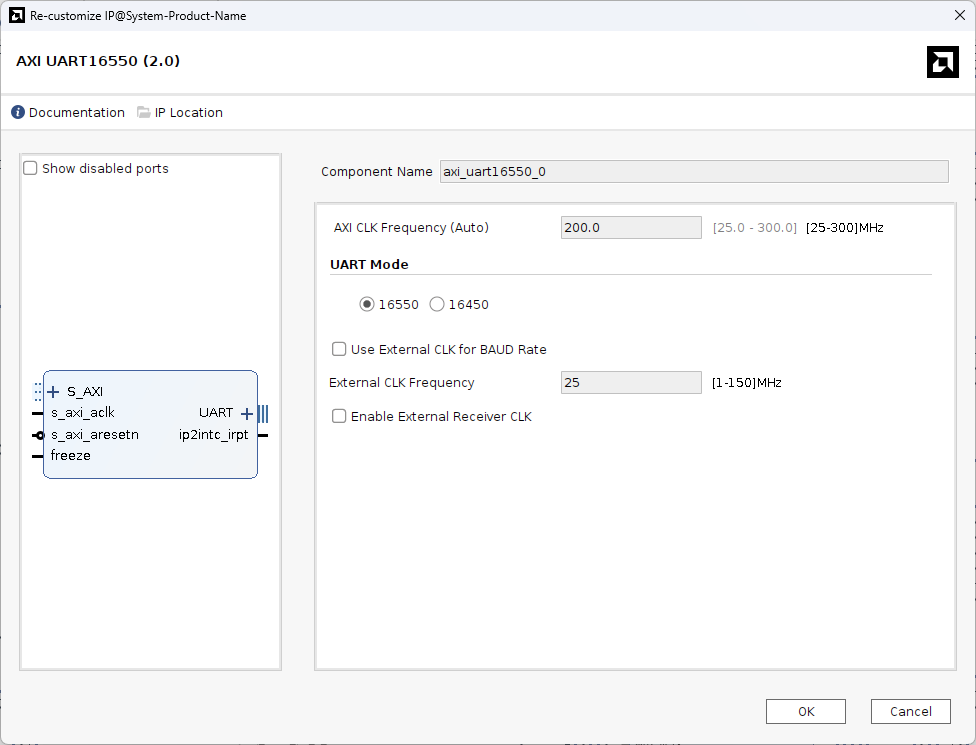

添加两个 AXI_UART16550 模块

PL 系统时钟是 200MHz

导出引脚,外接两个 RS485 外设。

添加后续几个 AXI_GPIO 模块控制 PL 端按键和 LED

Extender 模块是 ALINX 的检测 FMC 以及 40 pin 扩展口上引脚的代码模块,这里的 17 对引脚是 40pin 扩展口上引脚两两环通做测试,需要用到 ALINX 内部测试模块。

最后使用 AXI_Interconnect 模块将以上 16 个 AXI 模块连线。

(注意:ps_hello 工程中不涉及到 ps 和 pl 部分交互的接口,例如 hp 口,如果后续要在 pynq 系统中使用这部分接口,需要在这一步就将这些接口使能。移植完成的 pynq 系统中 ps 部分开放的接口和参数都是固定的,虽然基于 pynq 系统,可以任意重新配置 pl 部分,但 pl 能够和 ps 部分连接的接口在这一步就已经固定了。)

编译 vivado 工程,因为涉及 PL 侧部分导出包含 bit 流的 xsa

petalinux 工程

这部分可参考 ALINX 教程:

《course_s3_ALINX_ZYNQ_MPSoC 开发平台Linux 基础教程》“第一章 使用 Petalinux 定制 Linux 系统” 和 “第八章 SD 卡根文件系统”

使用上一章节导出的 xsa 搭建 petalinux 工程

设置离线编译和 sd 卡根文件系统

在设备树文件 system-user.dtsi 中修改成如下所示

/include/ "system-conf.dtsi"

/ {

clock_ref_pcie:clk100 {

compatible = "fixed-clock";

#clock-cells = < 0 >;

clock-frequency = < 100000000 >;

};

clock_ref_usb0:clk26 {

compatible = "fixed-clock";

#clock-cells = < 0 >;

clock-frequency = < 26000000 >;

};

clock_ref_dp:clk27 {

compatible = "fixed-clock";

#clock-cells = < 0 >;

clock-frequency = < 27000000 >;

};

};

&psgtr {

/* nc, sata, usb3, dp */

clocks = < &clock_ref_pcie >, < &clock_ref_usb0 >, < &clock_ref_dp >;

clock-names = "ref0", "ref1", "ref2";

};

&qspi {

status = "okay";

flash0: flash@0 {

#address-cells = < 1 >;

#size-cells = < 1 >;

compatible ="jedec,spi-nor";

reg= < 0x0 >;

partition@0 {

label = "qspi-0";

reg = < 0x000000000x02000000 >;

};

/delete-node/ partition@1;

/delete-node/ partition@2;

};

};

/* SD */

&sdhci1 {

disable-wp;

no-1-8-v;

};

/* USB */

&dwc3_0 {

status = "okay";

dr_mode = "host";

};

如果要用到 ps 部分的 m.2 接口,测试 ssd 固态硬盘,可以输入命令打开内核配置界面,在 Device Drivers ---> NVME Support --->路径下,按 y 使能 nvme 驱动<*> NVM Express block device 后,保存配置并退出

petalinux-config -c kernel

编译 petalinux 工程,生成 linux 镜像文件(BOOT.bin、boot.scr、image.ub、rootfs.tar.gz)

制作启动系统的 sd 卡,连接板卡的 ps 网口、dp 接口。板卡插上 u 盘、ssd 固态硬盘,uart 接口连接到主机,主机上打开串口终端。

板卡上电,串口终端打印启动信息,启动信息打印完成会提示输入用户名

2024.1 版本的 petalinux 系统默认用户名是 petalinux,初次登录会提示设置密码

测试功能接口

测试 ps 网口:如果网口是连接到支持 dhcp 服务的接口或者路由器,使用 ifconfig 命令可以查看到自动分配的 ip 地址,可以使用 ping 命令实际测试一下

测试 dp 接口:由于没有配置桌面环境,dp 接口连接到的显示器会显示另一个终端界面信息

测试 usb 接口:输入命令“ dmesg |grep usb ”,可以看到识别到了对应的 usb 设备,如图可以看到我插入的金士顿的 u 盘设备

测试 m.2 接口:输入命令“ ls /dev/nvme* ”,如果存在 nvme0,则说明识别到 ssd 设备

确认 petalinux 工程生成的系统 ps 部分的功能正常后,我们需要生成 bsp 包

由于 2024.1 版本的 petalinux 工具存在的一些 bug,似乎会将工作目录错误定位到系统根目录,该版本直接打包 bsp 会出现如下报错

一种解决方法是,在 ubuntu 的根目录下创建一个 build 目录并添加访问权限,用于通过 bsp 打包的过程检测,最终打包文件不受影响

sudo mkdir -p /build sudo chmod 777 /build

sudo mkdir -p /build最后成功打包生成 bsp

pynq 工程

在 home 目录下打开终端,输入命令,创建 pynq 的工作目录

mkdir -p /home/alinx/Projects/pynq

输入命令,切换到工作目录,下载 pynq 工程

cd /home/alinx/Projects/pynq git clone https://github.com/Xilinx/PYNQ.git

输入命令,运行 pynq 的环境配置脚本(该脚本只需要执行一次)

cd /home/alinx/Projects/pynq/PYNQ/sdbuild/scripts ./setup_host.sh

在 /home/alinx/Projects/pynq/PYNQ/boards 目录下创建一个新目录 AXU15EGB,用于存放对应开发板的配置文件,将之前 petalinux 工程生成的 petalinux.bsp 文件拷贝到该目录下

输入命令,创建并打开一个配置文件 AXU15EGB.spec

touch AXU15EGB.spec gedit AXU15EGB.spec

touch AXU15EGB.spec修改 AXU15EGB.spec 文件内容如下

ARCH_AXU15EGB := aarch64 BSP_AXU15EGB := petalinux.bsp #BITSTREAM_AXU15EGB := base/base.bit FPGA_MANAGER_AXU15EGB := 1 STAGE4_PACKAGES_AXU15EGB := xrt pynq ethernet pynq_peripherals

由于 AXU15EGB 板卡上 mmc0 设备对应的是 emmc,mmc1 对应的是 sd 卡

我们现在需要使用 sd 卡启动,所以需要将 /PYNQ/sdbuild/boot/meta-pynq/recipes-bsp/device-tree/files/pynq_bootargs.dtsi 文件中的 mmcblk0p2 改为 mmcblk1p2

将资源链接提供的三个预编译文件拷贝到 /PYNQ/sdbuild/prebuilt 目录下

输入命令,切换到 sdbuild 目录,配置 vitis 和 petalinux 的环境变量,编译 pynq 工程,编译过程中会有几次需要输入用户密码。(工程编译时间较长,编译时会从 github 上下载一些资源,如果网络稳定性较差,编译可能会失败)

cd /home/alinx/Projects/pynq/PYNQ/sdbuild source /opt/pkg/petalinux/settings.sh source /tools/Xilinx/Vitis/2024.1/settings64.sh make BOARDS=AXU3EGB

如果是网络问题导致的编译失败,比如访问 github 下载某些资源失败,可以重新输入“ make BOARDS=AXU15EGB ”编译

如果是其他报错,可以考虑输入命令“ make clean ”清除编译结果,然后重新编译工程

编译成功后会在 /PYNQ/sdbuild/output 目录下生成对应板卡型号的 img 镜像文件

运行测试

将镜像文件烧写到 sd 卡

烧写后的 sd 卡在 ubuntu 中可以看到两个分区,PYNQ 分区存放启动镜像,root 分区存放根文件系统,其中 root 分区由于是 EXT4 格式,在 windows 下一般是看不到的。

在 root 分区的 /usr/local/bin/ 目录下有一个 resizefs.sh 脚本,这个脚本会在系统初次启动时被执行,用于将 root 分区扩容到当前存储设备容量上限

在该目录下打开终端,输入命令,以 root 权限编辑文件,将里面的 mmcblk0 修改为 mmcblk1,保存文件并退出

sudo gedit resizefs.sh

开发板接上 dp 接口,ps 网口,uart 接口,插入 sd 卡,上电启动

此时串口终端会打印启动信息,完成启动后会自动登录(用户名和密码都是xilinx)

在串口终端中输入 ifconfig,确定 ps 网口分配到的 ip 地址,并确保主机和开发板能够双向 ping 通

在主机中打开浏览器,在网址栏输入:开发板 ip 地址:9090 ,回车确认。输入密码:xilinx,点击 Log in

此时会远程连接开发板上运行的 pynq 系统,并进入 jupyter 界面

dma 环通读写测试

本节测试用例参考文档

https://discuss.pynq.io/t/tutorial-pynq-dma-part-1-hardware-design/3133

https://discuss.pynq.io/t/tutorial-pynq-dma-part-2-using-the-dma-from-pynq/3134

搭建 AXU15EGB 的 dma 环通测试 vivado 工程,具体可以参考资源链接提供的 dma_test vivado 工程

在 sd 卡 root 分区 /home/xilinx/jupyter_notebooks 目录下创建一个 testfile 目录

将 vivado 工程 /dma_test/dma_test.runs/impl_1 目录下的 design_1_wrapper.bit 文件和 /dma_test/dma_test.gen/sources_1/bd/design_1/hw_handoff 目录下的 design_1.hwh 文件拷贝到 testfile 目录下,将 design_1.hwh 文件改名为 design_1_wrapper.hwh,和 bit 文件保持一致

将资源链接提供的测试程序 dma_test.ipynb 拷贝到 testfile 目录下

sd 卡插到板卡中,上电启动,查看 ip 地址。主机通过浏览器远程登录 pynq 系统,可以看到我们创建的 testfile 目录

点击 testfile 目录下的 dma_test.ipynb 程序,进入程序编写和执行界面

鼠标选中第一段程序,然后点击“运行”,这一段程序的功能是重新加载 bit 流,然后输出新 bit 流中各 ip 的配置状况,可以看到 dma 测试工程中的 axi_dma ip 的配置

当第 1 段执行完成,选中框会自动移动到下一段,我们可以多次点击运行,逐步执行程序

第 2 段是查询 axi_dma ip 是否存在,如果存在则输出它的帮助信息

第 3 段创建两个 dma 收发通道实例

第 4、5、6 段申请一段内存地址 input_buffer,并填充数据

第 7 段开始 dma 传输,第 8 段先申请一段内存地址 output_buffer 并打印其中部分数据,第 9、10 段接收 dma 传输过来的数据,并打印部分数据,可以看到和发送的数据一致。

资源链接

百度网盘:

https://pan.baidu.com/s/1J1KnN_z404Skze42CUj7gQ

提取码: in8s

- 随机文章

- 热门文章

- 热评文章

- 再现回升!一季度中国中小企业发展指数为89.3

- 西部计划: 重燃“到祖国最需要的地方去”激情

- 投资上海•共享未来——2024年“投资上海”广告产业推介会召开

- 巴基斯坦一周来暴雨灾害已造成至少87人死亡

- 扎心!多名美联储决策者一致发声:年内不降息

- 兰州银行副行长王斌国辞任,将出任兰州金控董事长

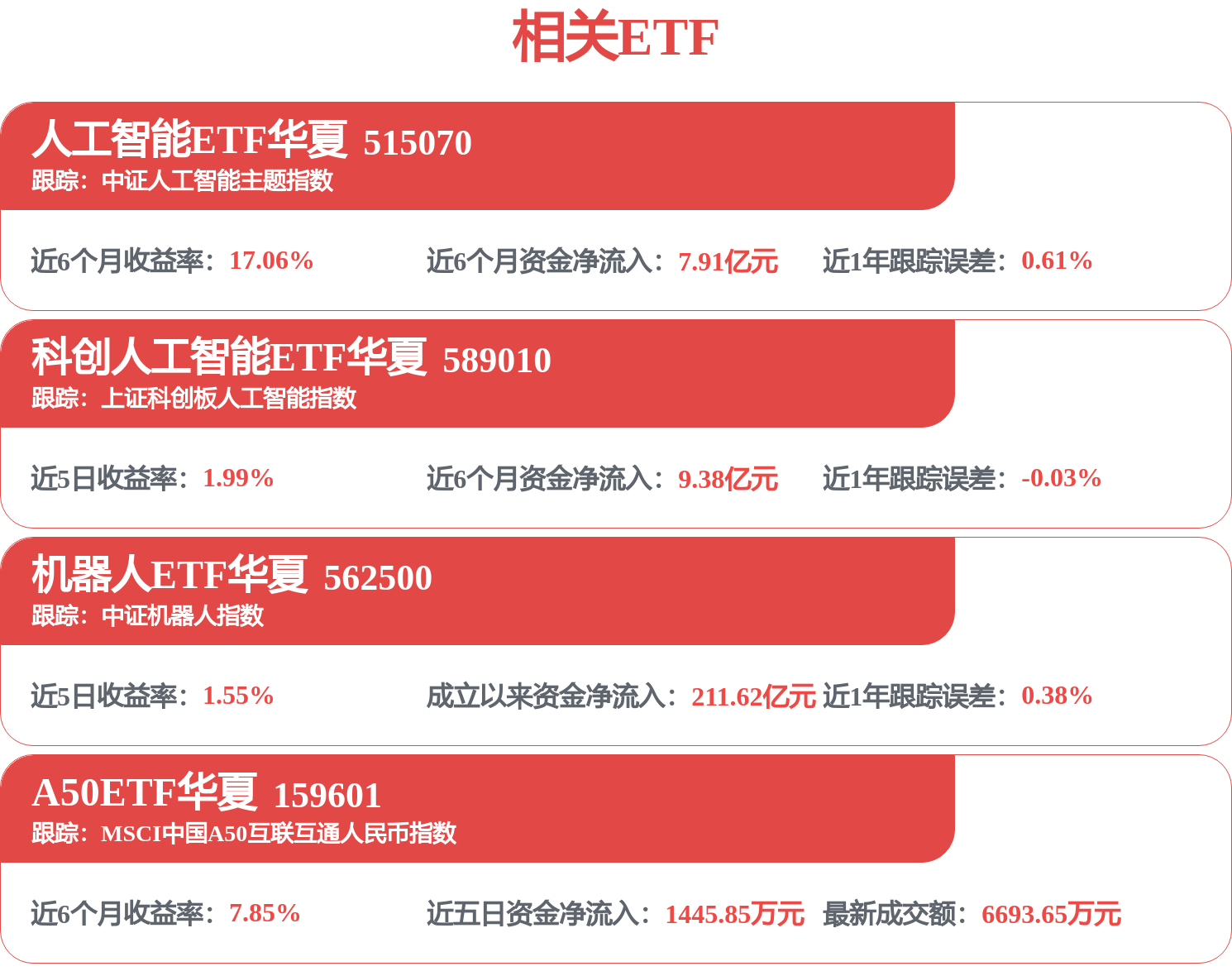

- 英伟达闪崩,沪深300跑赢纳指,那些人工智能基金怎样了?

- 突发!上市首日,茶百道暴跌30%!

- 浙江休闲农业去年接待3.6亿人次 营业收入达471亿元

- 涉嫌试图推翻2020年美总统竞选结果 多人受重罪指控

- 信达澳亚基金规模缩水逾百亿,债券产品为何拖了后腿?

- 今天,这串警号,全城呼叫!

- 微软全球资深副总裁张祺:AI大航海时代,人人都将拥有自己的Copilot

- 1“赛事+”提升城市“流量” 陕西商洛拓经济发展新“赛道”

- 2“五一”临近 持基过节的投资者要注意这几点

- 3华发股份:成功入选“人民优选”品牌 五一黄金周热销30亿

- 4钟鼓楼老街区的古都新事

- 5金税四期试点上线,财税体制改革拉开帷幕!或有资金借道信创ETF基金(562030)逢跌进场布局

- 6非常危险!女子摔成粉碎性骨折!又是因为洞洞鞋,夏天多人中招……

- 7到2027年产业规模达到2000亿元 浙江发布历史经典产业高质量发展计划

- 8初步数据:我国一季度经常账户顺差392亿美元

- 9IDC:24Q1全球PC出货量恢复增长 达到疫情前水平

- 10“发现山西之美”TDC旅游发现者大会举办:共话文旅新生态 邀客体验新玩法

- 11国门“夫妻档” 国庆共坚守

- 12北交所一周审核动态:2家企业更新进展 胜业电气二轮问询回复中称家电头部客户对价格敏感度较低

- 13(中国新貌)“国宝”大熊猫:栖居更美境 云游更广天

- 1大裁员下,特斯拉两名顶级高管离职

- 2奇瑞将与欧洲高端品牌签署技术平台授权协议

- 32024中国长三角青年企业家交流大会在杭州举办

- 4雷克萨斯GX中东版 全部在售 2023款 2022款 2020款 2019款 2018款成都远卓名车雷克萨斯GX中东版团购钜惠20万 欢迎上门试驾

- 5零跑C16将搭载中创新航磷酸铁锂电池

- 6Q1净利微增7%,宁德时代股东总数较2023年年末减少10728户

- 7哪吒,需要背水一战

- 8“新”中有“机”!创新服务承接新流量 撬动消费升级

- 9非创始版SU7何时交付 小米:工厂生产爬坡 全力提高产能

- 10央媒评卧铺挂帘:谁买的票谁做主

- 11江西南昌首部“多规合一”国土空间总体规划获批

- 12方程豹旗舰硬派越野!豹8正式亮相:仰望U8“青春版”登场

- 13583家族/造型霸气 方程豹豹8量产版发布